#### US007339559B2

# (12) United States Patent

# Yokoyama

# (54) COLOR ELECTROLUMINESCENCE DISPLAY DEVICE

(75) Inventor: **Ryoichi Yokoyama**, Ohgaki (JP)

(73) Assignee: Sanvo Electric Co., Ltd. (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 751 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 10/740,212

(22) Filed: Dec. 17, 2003

(65) **Prior Publication Data**

US 2004/0130514 A1 Jul. 8, 2004

# Related U.S. Application Data

(60) Division of application No. 10/132,546, filed on Apr. 25, 2002, now Pat. No. 6,690,118, which is a continuation of application No. 09/451,453, filed on Nov. 30, 1999, now Pat. No. 6,429,599.

### (30) Foreign Application Priority Data

| Dec. 1, 1998  | (JP) | <br>10-341860 |

|---------------|------|---------------|

| Sep. 30, 1999 | (JP) | <br>11-279875 |

- (51) **Int. Cl. G09G 3/30** (2006.01)

See application file for complete search history.

#### (56) References Cited

## U.S. PATENT DOCUMENTS

4,904,989 A 2/1990 Matsui et al.

# (10) Patent No.: US 7,339,559 B2

# (45) **Date of Patent:** \*Mar. 4, 2008

| 5,159,476 A   | 10/1992 | Hayashi              |

|---------------|---------|----------------------|

| 5,177,406 A * | 1/1993  | Troxel1 315/169.1    |

| 5,384,517 A   | 1/1995  | Uno 315/169.3        |

| 5,399,936 A   | 3/1995  | Namiki et al 313/504 |

| 5,550,066 A   | 8/1996  | Tang et al 437/40    |

#### (Continued)

#### FOREIGN PATENT DOCUMENTS

EP 0 717 445 A2 6/1996

# (Continued)

## OTHER PUBLICATIONS

Notice of Grounds For Rejection, Patent Application Serial No. Hei 11-279875, mailed Aug. 27, 2002.

#### (Continued)

Primary Examiner—Lun-Yi Lao (74) Attorney, Agent, or Firm—Cantor Colburn LLP

#### (57) ABSTRACT

An electroluminescence display device is provided in which a plurality of pixels are arranged in row and column directions, including: a gate line extending in the row direction; a first thin film transistor whose gate is connected to the gate line; a drain line extending in the column direction; a capacitor connected to the drain line via the first thin film transistor; a second thin film transistor whose control electrode is connected to the capacitor; and an EL element connected to a supply line via the second thin film transistor and having a luminescent layer between an anode and a cathode. The first thin film transistor is disposed in a region between the gate line and the capacitor.

#### 1 Claim, 7 Drawing Sheets

| U.S. PATENT                        | DOCUMENTS                | JP 8-43859 2/1996                                                    |

|------------------------------------|--------------------------|----------------------------------------------------------------------|

|                                    |                          | JP 8-227276 9/1996                                                   |

|                                    | Utsugi et al             | JP 9-274202 10/1997                                                  |

|                                    | Tang et al 315/169.3     | WO WO 97/38445 10/1997                                               |

|                                    | Nagayama et al 315/167   | WO WO98/36406 2/1998                                                 |

|                                    | Utsugi et al 315/504     | WO WO 98/36407 8/1998                                                |

|                                    | Matsuo                   |                                                                      |

|                                    | Saito et al 345/79       | OTHER PUBLICATIONS                                                   |

| 5,852,481 A 12/1998                | Hwang 349/43             |                                                                      |

|                                    | Yamauchi et al 438/29    | European Search Report for Application No. 99309642.9-2203           |

|                                    | Jones 257/40             | dated Nov. 18, 2004.                                                 |

|                                    | Matsuo 349/38            | European Search Report for Application No. 99309646.0-2203           |

|                                    | Yamada et al 315/169.3   | dated Nov. 18, 2004.                                                 |

|                                    | Kijima 428/690           | Excerpt English translation of Japanese Patent Laid-Open Publica-    |

| 6,133,693 A 10/2000                | Keyser 313/506           | tion No. Hei 2-245740.                                               |

|                                    | Shibata et al 313/506    | Excerpt English translation of Japanese Patent Laid-Open Publica-    |

| 6,175,345 B1 1/2001                | Kuribayashi et al 345/76 | tion No. Hei 7-6875.                                                 |

| 6,281,634 B1* 8/2001               | Yokoyama 315/169.3       | Excerpt English translation of Japanese Patent Laid-Open Publica-    |

| 6,429,599 B1 8/2002                | Yokoyama 315/169.3       | tion No. Hei 8-227276.                                               |

| 6,462,724 B1 10/2002               | Ozawa et al.             | Excerpt English translation of Japanese Patent Laid-Open Publica-    |

| 6,522,315 B2 2/2003                | Ozawa et al.             | tion No. Hei 8-43859.                                                |

| 6,674,106 B2 1/2004                | Tanaka et al.            | Excerpt English translation of Japanese Patent Laid-Open Publica-    |

| 6,690,118 B2 * 2/2004              | Yokoyama 315/169.3       | tion No. Hei 9-274202.                                               |

| 6,839,045 B2 1/2005                | Ozawa et al.             | Excerpt English translation of Japanese Patent Laid-Open Publica-    |

| 2002/0196206 A1 12/2002            | Kimura et al.            | tion No. Sho 58-140781.                                              |

| 2003/0098827 A1 5/2003             | Ozawa et al.             | Fletcher, Peter: "Flat Polymer Display Promises TV-Quality Pic-      |

| 2003/0231273 A1 12/2003            | Kimura et al.            | tures Two Years Sooner Than Expected" Electronic Design, Penton      |

| 2004/0150591 A1 8/2004             | Ozawa et al.             | Publishing, Cleveland, OH, US, vol. 46, No. 8, Apr. 6, 1998 p. 35,   |

|                                    |                          | column 3, line 8-line 24.                                            |

| FOREIGN PATE                       | NT DOCUMENTS             |                                                                      |

| EP 0 717 446 A2                    | 6/1996                   | Notice of Grounds for Rejection for Japanese Patent Application      |

| EP 0 717 440 A2<br>EP 0 880 303 A1 | 11/1998                  | Serial No. Hei 11-281789 dated Aug. 27, 2002.                        |

| EP 0 895 219 A1                    | 2/1999                   | Japanese Patent Laid-Open Publication No. Hei 10-92574 with          |

|                                    |                          | English abstract Japanese Patent Laid-Open Publication No. Hei       |

| JP 58-140781                       | 8/1983                   | 10-289784 with English abstract Japanese Patent Laid-Open Pub-       |

| JP 2-176725                        | 7/1990                   | lication No. Hei 8-227276 with English abstract.                     |

| JP 2-245740                        | 10/1990                  | Office Action in connection with a related Japanese application, No. |

| JP 6208131                         | 7/1994                   | Hei 11-281789, issued on Dec. 21, 2004.                              |

| JP 6308536                         | 11/1994                  | * aited by evenings                                                  |

| JP 7-6875                          | 1/1995                   | * cited by examiner                                                  |

Fig. 1

(PRIOR ART)

Fig. 2 (PRIOR ART)

Fig. 3 (PRIOR ART)

G B R G B R G 8 GB R GB RG B Fig. 4A GB R G B RGB GB R GB R G B Fig. 4B 70 RGBRGB GB G| B | R | G | B | R | G | B | R | G Fig. 4C RGBRGBRGB GBRGBRGBRG Fig. 4D

Fig. 6A

Fig. 6B

Fig. 7

1

# COLOR ELECTROLUMINESCENCE DISPLAY DEVICE

# CROSS-REFERENCE TO RELATED APPLICATION

This application is a division of U.S. patent application Ser. No. 10/132,546, filed Apr. 25, 2002 now U.S. Pat. No. 6,690,118, the entire contents of which are incorporated herein by reference, which is a continuation of U.S. patent 10 application Ser. No. 09/451,453, filed Nov. 30, 1999 now U.S. Pat. No. 6,429,599, the entire contents of which are incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to an active type color EL (electroluminescence) display device in which an electroluminescence (EL) element is driven using a thin film transistor (TFT).

#### 2. Description of Related Art

Practical use of organic EL elements in next generation display devices is greatly expected, because such displays can eliminate need for a back light as required in a liquid 25 crystal display device for self-emission, can be optimally made thin, and can have an unlimited viewing angle.

Three methods have commonly been proposed for achieving color display in a display device comprising such an organic EL element.

In the first method, different emissive materials for each of the primary RGB colors are used in corresponding emissive layers to individually form discrete color pixels directly emitting respective RGB light rays. In another method, an emissive layer generates white luminescence 35 which is then converted into three primary colors using color filters. A third method is based on conversion of light from a blue emissive layer into three primary colors using color conversion mediums (CCM). As light energy is lost in the second and third methods above due to the use of color filters or color conversion mediums, the first method is the most effective of these in this respect because a desired light ray is directly emitted.

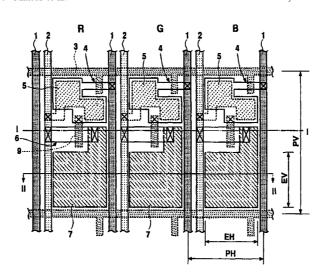

Meanwhile, to drive an organic EL display device, two types of driving methods, a passive type using a passive 45 matrix and an active type employing TFTS, are available. The circuit configuration shown in FIG. 1 may be used in an active display.

FIG. 1 illustrates a circuit configuration for a single pixel in such a display pixel. Each pixel comprises an organic EL 50 element **20**, a first TFT **21** for switching, in which a display signal DATA is applied to a drain and a scan signal SCAN is applied to a gate to switch the TFT on and off, a capacitor **22** which is charged by a display signal DATA applied when the TFT **21** is on and which holds a charge voltage Vh when 55 the TFT **21** is off, a second TFT **23** in which a drain is connected to a drive source of a voltage V<sub>COM</sub>, a source is connected to an anode of the organic EL element **20** and a hold voltage Vh is applied to a gate from the capacitor **22** to drive the organic EL element **20**.

A scan signal SCAN rises to an H level during one horizontal scanning period (1H). When the TFT 21 is switched on, a display signal DATA is applied to one end of the capacitor 22, which is then charged by a voltage Vh corresponding to the display signal DATA. This voltage Vh 65 remains held in the capacitor 22 for one vertical scanning period (1V) even after the signal SCAN becomes a low level

2

to switch the TFT **21** off. Because the voltage Vh is supplied to the gate of the TFT **23**, the EL element is controlled so as to emit light with a luminance in accordance with the voltage Vh.

The conventional configuration of such an active type EL display device for achieving color display by means of the above-mentioned first method will be now described.

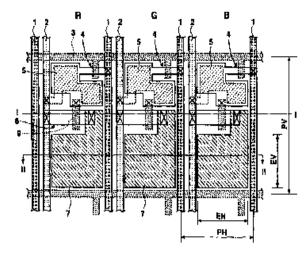

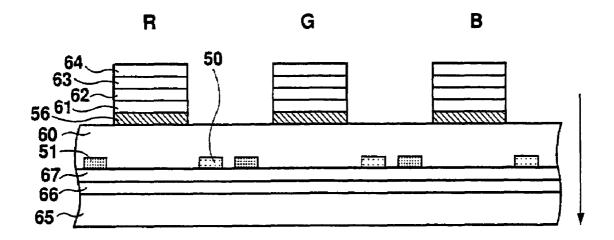

FIG. 2 depicts a conceptual plan view showing a configuration of a related art device, and FIG. 3 is a cross section taken along line III-III in FIG. 2. Each of the drawings depicts three pixels.

In FIGS. 2 and 3, numeral 50 represents a drain line for supplying a display signal DATA, numeral 51 represents a drive source line for supplying a supply voltage  $V_{COM}$ , and 15 numeral 52 represents a gate line for supplying a scan signal SCAN. Further, numerals 53, 54, and 55 designate features corresponding the first TFT 21, the capacitor 22, and the second TFT 23 in FIG. 1, respectively, and numeral 56 designates an anode of the EL element 20 which constitutes a pixel electrode. As shown, discrete anodes 56 are separately formed for each pixel on a planarization insulating film 60. A hole-transport layer 61, an emissive layer 62, an electron-transport layer 63, and a cathode 64 are sequentially laminated on the discrete anode 56, thereby forming an EL element. Holes injected from the anodes 56 and electrons injected from the cathodes 64 are recombined inside the emissive layer 62, which emits light in the direction of the transparent anodes toward outside, as shown by arrows in FIG. 3. Here, discrete hole-transport layers 61, discrete emissive layers 62 and discrete electron-transport layers 63 having substantially the same shape as the discrete anodes 56 are provided for respective pixels. Emissive materials which are different for each RGB are used in the corresponding emissive layers 62, and therefore light rays having respective RGB colors are emitted from respective EL elements. The cathode 64, which applies a common voltage to each pixel, extends over the pixels. Partitions 68 are interposed between adjoining emissive layers 62. Further, numerals 65, 66, and 67 designate a transparent glass substrate, a gate insulating film, and an interlayer insulating film, respectively.

However, the arrangement of the first TFT 53, the capacitor 54, the second TFT 55, and the anode 56 of the related examples do not take sufficient consideration of integration efficiency and therefore a more highly-integrated configuration is in demand.

Further, the color display device generally adopts a stripe arrangement as shown in FIG. 4A or a delta arrangement as shown in FIG. 4C as an arrangement for three primary colors of RGB. At the same time, it is necessary to use different luminescent materials for each of RGB such that discrete EL elements can directly emit light rays of respective RGB colors. Therefore, if the stripe arrangement shown in FIG. **4**A is adopted, for example, a metal mask **70** shown in FIG. 4B may be used to form the luminescent layers as follows. First, a luminescent layer for R is formed by evaporating only an R color luminescent material onto the hole transport layer. Then, the metal mask 70 is displaced by a distance corresponding to one pixel in the horizontal direction to 60 form a luminescent layer for G by evaporating only a G color luminescent materials on the hole transport layer. Finally, the metal mask 70 is further displaced by one pixel in the horizontal direction to form a luminescent layer for B by evaporating only a B color luminescent material. In the case of the delta arrangement shown in FIG. 4C, the luminescent layers can be similarly formed using the metal mask shown in FIG. 4D.

3

However, during the process for forming the luminescent layers by evaporating the luminescent materials, a so-called "diffusion" phenomenon is caused in which luminescent materials are deposited onto regions other than the regions directly under the openings in the metal masks 70 and 71. 5 Because of such diffusion phenomenon or because of imperfect construction of the metal mask itself, colors in adjoining pixels are adversely mixed causing color purity to deteriorate. Particularly in delta arrangements, wherein adjoining pixels in the column and row directions differ from one 10 another, this disadvantage is further pronounced.

#### SUMMARY OF THE INVENTION

The present invention provides a color display device 15 suitable for a highly integrated configuration.

In accordance with one aspect of the present invention, a first thin film transistor is disposed in a region between a gate line and a capacitor, and a second thin film transistor is disposed in a region between the capacitor and an EL <sup>20</sup> element. This configuration allows the capacitor, the first thin film transistor, and the second thin film transistors to be densely arranged, thereby facilitating formation of a highly integrated configuration.

In accordance with another aspect of the present invention, said first thin film transistor is connected to one end of one electrode of said capacitor while a gate of said second thin film transistor is connected to the other end which is opposed to said one end of the capacitor. Thus, the first thin film transistor and the gate of the second thin film transistor are electrically connected via the one electrode of the capacitor.

In accordance with still another aspect of the present invention, the capacitor includes a dent region in which the first thin film transistor is disposed. Thus, an efficient <sup>35</sup> arrangement can be achieved.

In accordance with still another aspect of the present invention, the EL element includes a dent region in which the second thin film transistor is disposed. Thus, an efficient arrangement can be achieved.

In accordance with further aspect of the present invention, the capacitor and the EL element are disposed so as to adjoin each other in the column direction, such that space is provided in the vertical direction. Therefore, when forming a pixel electrode (for example, an anode), color mixture among adjoining pixels can be prevented, when metal mask positioning accuracy is low, thereby maintaining preferable color purity for even highly detailed displays.

### BRIEF DESCRIPTION OF THE DRAWINGS

These and other objects of the invention will be explained in the description below, in connection with the accompanying drawings, in which:

FIG. 1 is a view showing a circuit configuration of an  $^{55}$  active type color EL display device.

FIG. 2 is a plan view showing a configuration of a conventional color EL display device;

FIG. 3 is cross section showing a configuration of a  $_{60}$  conventional color EL display device;

FIGS. 4A, 4B, 4C and 4D are views for explaining color arrangements used in a color EL display device;

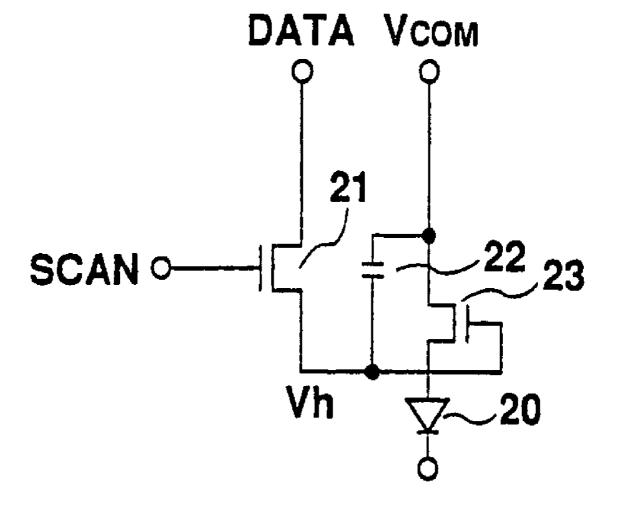

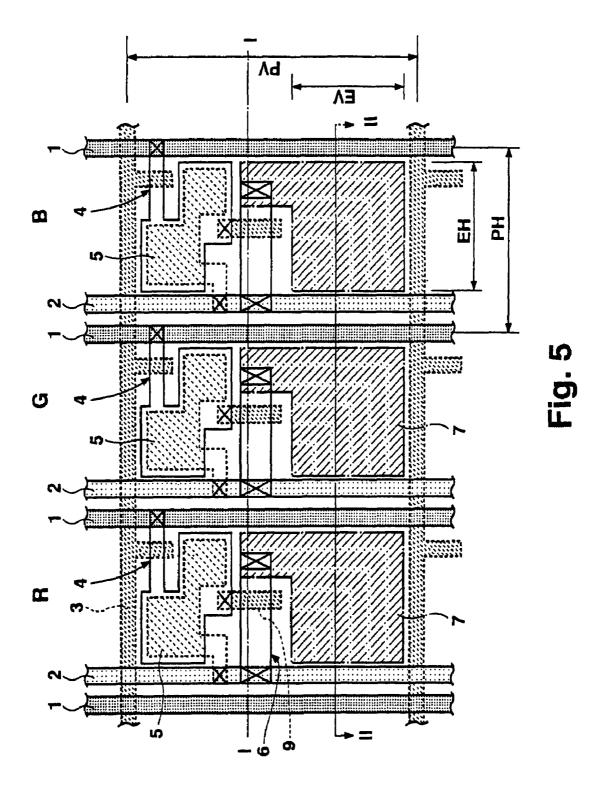

FIG. 5 is a plan view illustrating a first embodiment of the present invention;

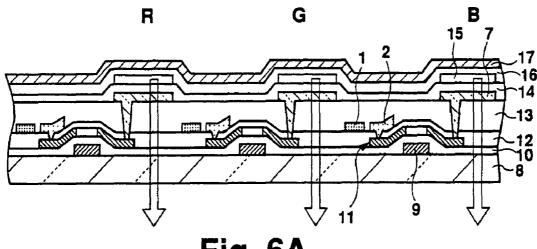

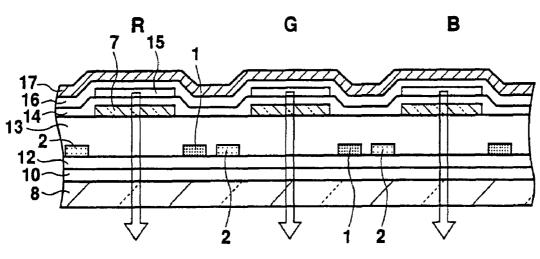

FIGS. 6A and 6B are cross sections illustrating the first embodiment of the present invention; and

4

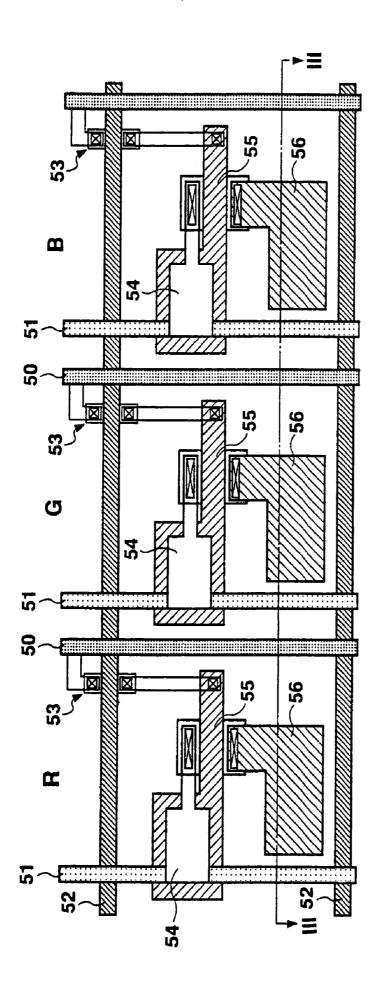

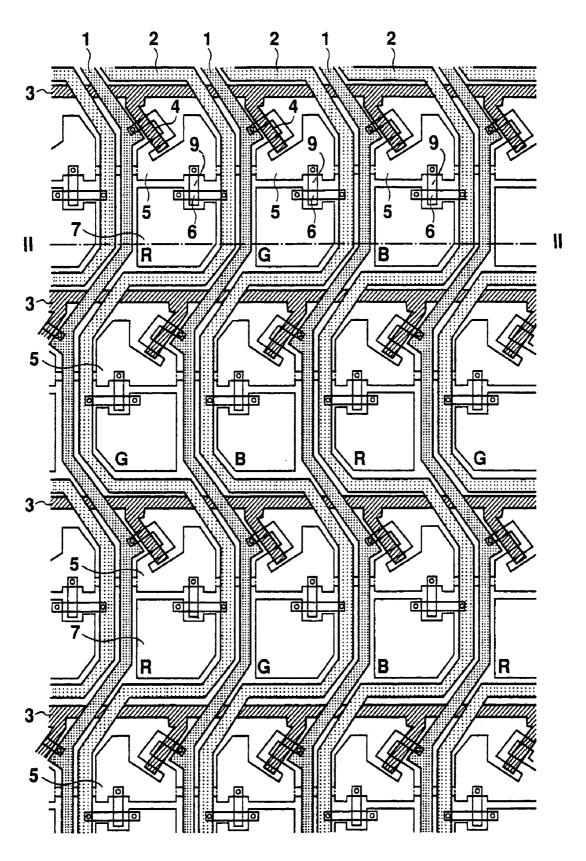

FIG. 7 is a plan view illustrating a second embodiment of the present invention.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

FIG. 5 is a plan view showing a color EL display device in accordance with a first embodiment of the present invention, and depicts the configuration corresponding to three pixels of RGB. Further, FIG. 6A is a cross section taken along a line I-I of FIG. 5, and FIG. 6B is a cross section taken along a line II-II of FIG. 5. This embodiment exemplifies a configuration for the stripe pixel arrangement shown in FIG. 4A.

A driving circuit for each pixel in this embodiment is the same as that in FIG. 1, and the configuration of the device differs from the example shown in FIGS. 2 and 3 in the pattern arrangement and the cross section.

Referring to FIGS. 5, 6A and 6B, the device comprises a data line 1 made of aluminum for supplying a display signal DATA, a power supply line 2 made of aluminum for supplying a power from a drive source COM, and a gate line made of chrome for supplying a scan signal SCAN. Each pixel of the EL display further comprises a first TFT 4 corresponding to the first TFT 21 in FIG. 1, a capacitor 5 corresponding to the capacitor 22 in FIG. 1, a second TFT 6 corresponding to the second TFT 23 in FIG. 1, and an anode (a first electrode) 7 of the EL element 20 comprising ITO and constituting an pixel electrode. In FIG. 5, regions enclosed by dot lines are formed by chromium, regions enclosed by solid lines other than the data line 1 and the power supply line 2 are formed using a polysilicon thin film.

The second TFT **6** is formed as follows. First, a gate electrode **9** is formed on a transparent glass substrate **8**, and a gate insulating film **10** is formed thereupon. Then, a polysilicon thin film **11** formed on the gate insulating film **10** is covered with an interlayer insulating film **12**, on which the data line **1** and the power supply line **2** are formed. A planarization insulating film **13** is further formed thereon and the anode **7** comprising ITO is finally formed on the planarization insulating film **13**. Then, the drain region of the polysilicon thin film **11** is brought into contact with the power supply line **2** while the source region of the polysilicon thin film **11** is brought into contact with the anode **7**.

The configuration of the first TFT 4 is substantially the same as that of the second TFT 6, with the notable exception that the drain region of the first TFT 4 is connected to the data line 1, and not to the power supply line 2. Further, the capacitor 5 connected to the first TFT 4 comprises a chromium electrode and a polysilicon thin film having a gate insulating film interposed therebetween.

The discrete anodes 7 are formed on the planarization insulating film 13 corresponding to respective pixels, and a hole-transport layer 14 is formed thereon so as to cover the entire pixels. Then, discrete emissive layers 15 are formed for each pixel, on which an electron-transport layer 16 and a cathode 17 are laminated in this order to complete formation of an EL element. Holes injected from the anode 7 and electrons injected from the cathode 17 are recombined inside the emissive layer 15, which emits light in the direction of the transparent anode toward outside, as indicated by arrows in FIGS. 6A and 6B. The discrete emissive layers 15 are formed for respective pixels to have substantially the same shape as the discrete anodes 7, and different emissive materials are used for each of the RGB colors. Thus, each EL element emits one type of RGB light.

5

Materials of, for example, MTDATA, Alq<sub>3</sub>, and MgIn alloy may be used for the hole-transport layer **14**, the electron-transport layer **16**, and the cathode **17**, respectively. Further, for example, Alq containing DCM type as dopant is used for the emissive layer **15** for R, Alq containing quinacridon as dopant is used for the emissive layer **15** for G, and DPVBi containing distyrylarylene or Perylene as dopant is used in the emissive layer **15** for B.

In this embodiment, as in the first embodiment, the first TFT 4 is disposed in a region between the gate line 3 and the 10 capacitor 5, and the capacitor 5 includes a dent region in which the first TFT 4 is disposed. Further, the second TFT 6 is disposed in a region between the capacitor 5 and the anode 7, and the anode 7 includes a dent region in which the second TFT 6 is disposed. In other words, the capacitor 5 is 15 disposed in a middle area between first TFT 4 and second TFT 6. The capacitor 5 also functions as a wiring for connecting the first TFT 4 and the second TFT 6. Due to such configuration, it is possible to densely arrange the first TFT 4, the capacitor 5, the second TFT 6, and the anode 7, 20 thereby increasing the integration efficiency of pixels and achieving a highly detailed display.

FIG. 7 depicts, in plan view, the second embodiment of the present invention. In FIG. 7, the same elements as shown in FIGS. 1, 5 and 6 are designated by the same reference 25 numerals, and the detailed description thereof will be omitted. In FIG. 7, numeral 4 denotes a first TFT corresponding to the first TFT 21 of FIG. 1, numeral 5 denotes a capacitor corresponding to the capacitor 22 of FIG. 1, numeral 6 denotes a second TFT corresponding to the second TFT 23 30 of FIG. 1 and numeral 7 denotes an anode of the EL element 20 comprising ITO and constituting a pixel electrode. This embodiment exemplifies a configuration in the case of a delta pixel arrangement as shown in FIG. 4C.

In this embodiment, as in the first embodiment, the first 35 TFT 4 is disposed in a region between the gate line 3 and the capacitor 5, and the capacitor 5 includes a dent region in which the first TFT 4 is disposed. Further, the second TFT 6 is disposed in a region between the capacitor 5 and the anode 7, and the anode 7 includes a dent region in which the 40 second TFT 6 is disposed. The capacitor 5 also functions as a wiring for connecting the first TFT 4 and the second TFT 6. Due to such configuration, it is possible to densely arrange the first TFT 4, the capacitor 5, the second TFT 6, and the anode 7, thereby increasing the integration efficiency of 45 pixels and achieving a highly detailed display.

When a delta arrangement is used, pixels of different colors adjoin with one another in the column direction, as shown in FIG. 4C. In this embodiment, however, because the first TFT 4 and the capacitor 5 are disposed in the vertical 50 direction of the anode 7 which is a pixel electrode, gaps between the EL elements in the column direction can be sufficiently secured. As described above, by forming the pixel electrode 7 and the luminescent layer 15 with substantially the same shape, the luminescent region of a pixel and 55 the pixel electrode itself also have substantially the same shape. When this is the case, if the dimensions of the luminescent region in the horizontal and vertical directions are EH and EV, respectively, and that the dimensions of the pixel pitch in the horizontal and vertical directions are PH 60 and PV, respectively, the relationship EH/EV≥PH/PV will

6

hold. Because of this configuration, capacity against diffusion of the luminescent materials is increased in the vertical direction when forming the respective RGB luminescent layers using the metal mask, thereby reducing a possibility of color mixture even if the luminescent layers are formed with a manufacturing accuracy which is similar in the prior art

In a typical delta arrangement, pixels of the same color which are adjacent in the column direction are displaced from each other in the row direction by a distance corresponding to about 1.5 pixels. Therefore, the arrangement including such an 1.5 pixel displacement is preferably used in the present invention. However, the size of pixel displacement is not limited to 1.5 and the arrangement including an 1.2 pixel displacement as shown in FIG. 7 may be used.

According to the present invention, since the first thin film transistor is disposed between the gate line and the capacitor and the second thin film transistor is disposed between the capacitor and the EL element, it is possible to densely arrange these features so as to achieve a highly integrated configuration.

Further, color mixture in adjoining pixels which causes deterioration of color purity can be prevented in an active type color EL display device, thereby maintaining preferable color purity even in a highly detailed display.

Specifically, by disposing at least part of a capacitor or a thin film transistor in the horizontal direction of the luminescent region of each pixel, a room is provided in each pixel in the horizontal direction such that highly detailed display can be achieved even if accuracy in metal mask positioning is low.

Although the present invention is also applicable to a delta pixel arrangement, the above-mentioned effects especially work in a stripe arrangement.

What is claimed is:

- 1. An electroluminescence display device in which a plurality of pixels are arranged in row and column directions, comprising:

- a gate line extending in the row direction;

- a first thin film transistor whose gate is connected to said gate line;

- a drain line extending in the column direction;

- a capacitor connected to said drain line via said first thin film transistor;

- a second thin film transistor whose control electrode is connected to said capacitor; and

- an EL element connected to a supply line via said second thin film transistor and having a luminescent layer between an anode and a cathode,

- wherein said first thin film transistor is disposed in a region between said gate line and said capacitor,

- wherein said first and second thin film transistors are disposed on opposite sides with said capacitor in a middle area between said first and second thin film transistors wherein said first thin film transistor is connected to one end of an electrode of said capacitor, and a gate of said second thin film transistor is connected to the other end of said electrode of said capacitor.

\* \* \* \* \*

| 专利名称(译)        | 彩色电致发光显示装置                                                                                                                                              |         |            |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|

| 公开(公告)号        | <u>US7339559</u>                                                                                                                                        | 公开(公告)日 | 2008-03-04 |  |  |

| 申请号            | US10/740212                                                                                                                                             | 申请日     | 2003-12-17 |  |  |

| [标]申请(专利权)人(译) | 横山良一                                                                                                                                                    |         |            |  |  |

| 申请(专利权)人(译)    | 横山良一                                                                                                                                                    |         |            |  |  |

| 当前申请(专利权)人(译)  | SANYO ELECTRIC CO. , LTD.                                                                                                                               |         |            |  |  |

| [标]发明人         | YOKOYAMA RYOICHI                                                                                                                                        |         |            |  |  |

| 发明人            | YOKOYAMA, RYOICHI                                                                                                                                       |         |            |  |  |

| IPC分类号         | G09G3/30 G09F9/30 G09G3/32 H01L27/32 H01L51/50 H05B33/00 H05B33/12 H05B33/14                                                                            |         |            |  |  |

| CPC分类号         | G09G3/3225 H01L27/3211 H01L27/326 H01L27/3262 H01L27/3265 G09G2300/0417 G09G2300/0426 G09G2300/0465 G09G2300/08 G09G2300/0842 G09G2320/0214 H01L27/3276 |         |            |  |  |

| 代理机构(译)        | 康托科尔伯恩LLP                                                                                                                                               |         |            |  |  |

| 优先权            | 1998341860 1998-12-01 JP<br>1999279875 1999-09-30 JP                                                                                                    |         |            |  |  |

| 其他公开文献         | US20040130514A1                                                                                                                                         |         |            |  |  |

| 外部链接           | Espacenet USPTO                                                                                                                                         |         |            |  |  |

# 摘要(译)

提供一种电致发光显示装置,其中多个像素沿行和列方向排列,包括:沿行方向延伸的栅极线;第一薄膜晶体管,其栅极连接到栅极线;沿列方向延伸的排水管线;电容器通过第一薄膜晶体管连接到漏极线;第二薄膜晶体管,其控制电极连接到电容器; EL元件通过第二薄膜晶体管连接到电源线,并且在阳极和阴极之间具有发光层。第一薄膜晶体管设置在栅极线和电容器之间的区域中。